## VIKAS GROUP OF INSTITUTIONS

(Sponsored by Mother Theresa Educational Society) Approved by AICTE, New Delhi, PSI, New Delhi & Affiliated to JNTUK, Kakinada

ISO 9001: 2015 Certified

Nunna - 521 212, Vijayawada Rural, NTR District, A.P. India.

Email: principal.9t@gmail.com

# 3.3.1 Number of research papers published per teacher in the Journals as notified on UGC CARE list during

AY 2021

| S.No | Title of paper                                                                                                           | Name of the author/s | Department of the teacher | Calendar<br>Year of<br>publication |

|------|--------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------|------------------------------------|

| 1    | Design a High speed RIFFA based<br>Homomorphic Encryption<br>/Decryption                                                 | G.SEKHAR<br>REDDY    | Dept of ECE               | 2021                               |

| 2    | Design high Speed Efficient IVLSI<br>Architecture of E.R hybrid Adder                                                    | G SEKHAR<br>REDDY    | Dept of ECE               | 2021                               |

| 3    | Implementation of 32 and 32 dadda<br>multipier                                                                           | G.SEKHAR<br>REDDY    | Dept of ECE               | 2021                               |

| 4    | Design and implementation of high efficient delay utillisation of (n/2) parallel multiplier                              | G.SEKHAR<br>REDDY    | Dept of ECE               | 2021                               |

| 5    | Design and Implementation of triple<br>bit error correcting bch decoder with<br>high efficiency for emerging<br>memories | G.SEKHAR<br>REDDY    | Dept of ECE               | 2021                               |

| 6    | Design of efficient 32-bit vedic<br>multiplier                                                                           | G.SEKHAR<br>REDDY    | Dept of ECE               | 2021                               |

Vijayawada Rural, NTR Dist. A.F.

# DESIGN A HIGH SPEED RIFFA BASED HOMOMORPHIC ENCRYPTION/DECRYPTION

1K.ROJA, 2G SEKHAR REDDY

<sup>1</sup>M.Tech Scholar, Dept of ECE, Vikas Group of Institutions, Nunna, Vijayawada, Andhra Pradesh, India <sup>2</sup>Assistant Professor, Dept of ECE, Vikas Group of Institutions, Nunna, Vijayawada, Andhra Pradesh, India

ABSTRACT: In this project, design and implementation of high speed and high secure BFC based Homomorphic encryption is done. This system will provide better security and resource efficiency compared to existing standards. RIFFA based homomorphic encryption technique guarantee both privacy and integrity. The main intent is to increase the speed of operation. Initially, input bits and key is expanded serial by using PCIe. Next, bits are substituted using S-Box. After substitution of bytes, the bits will be reusable using RIFFA. After reusable procedure shifting operation is performed. Now these bits are encrypted. Similarly, decryption process is reverse to this operation.. Hence RIFFA based homomorphic encryption and decryption is implemented and it gives better security compared to exist one.

KEY WORDS: Homomorphic encryption, Large Integer Multiplication, Operand Reduction, VLSI Architecture, S-Box, Peripheral Component Interconnect express (PCIe), Reusable Integration Framework for FPGA Accelerators (RIFFA).

### I. INTRODUCTION

Fully Homomorphic Encryption is for the most part utilized in the database of the board frameworks (DMBS). One of the present issues related with the utilization of databases is the test of verifying and securely putting away the legitimate treatment of classified information in the remote database. Privacy of touchy data can be guaranteed using cryptography.

It may, be the utilization of industrious encryption calculations to store the data in remote databases can fundamentally decrease the presentation of the framework without interpreting. To take care of the issue, in MIT examines exhibited Crypto system.

Utilizing additively homomorphic crypto framework enables the server to execute SUM, AVG, and Count Questions over encoded information; the other SQL inquiries utilize the distinctive encryption calculations with the vital usefulness. The adjustment of completely homomorphic cryptosystem will keep the capacity to perform run of the mill database tasks on encoded information without decoding the information in a confided condition. In any case, such a cryptosystem must fulfill certain prerequisites for practical qualities and computational unpredictability, which is significant.

Fully Homomorphic Encryption (FHE) is a huge achievement in cryptographic research in recent years. A FHE plan can be utilized to elective perform calculations on figure content without trading off the substance of relating the plain text [1]. Therefore, a practical FHE plan will open the way to security advances and various new protection related to the applications, for example, security safeguarding pursuit and cloud-based processing. For the most part, FHE can be ordered into three classifications: cross section based, number based, and learning with mistakes.

One of the fundamental difficulties in the improvement of FHE applications is to moderate the amazingly high-computational intricacy and asset necessities [2-4]. For instance, programming usage of FHE in superior PCs still expend the critical calculation time, especially to achieve the vast whole number duplication which more

Volume XIII, Issue II, February/2021

VIKAS GROUP OF INSTITUTIONS

NUMBA - 521 212

Vijayawada Rural, NTR Dist., A.P.

often than not includes more than countless bits. For cross section based FHE, bit increase the required for the little setting with a grid measurement. To quicken the FHE tasks, different effective plans have been proposed to handle the extensive whole number duplication.

The objective of this paper is to revive the encryption natives in entire number based FHE using FPGA advancement. This particular FHE count is picked because of the less unpredictable theory, humbler key size and equivalent execution. Also, the introduction of a grouped FHE plots over the entire numbers ensures further capability upgrades. Augmentation is a key segment in these FHE plans the features in the encryption, unscrambling and evaluation steps. Broad entire number FFT duplication has furthermore been used in the late of referenced gear and GPU use of other FHE plans. Future work will look into the impact of the gear multiplier on substitute walks inside the FHE plot. Specifically, presenting the primary gear execution of encryption rough required for FHE over the numbers.

### II. EXISTED SYSTEM

The below figure (1) shows the architecture of existed system. In this system mainly, two NTT units, a controller unit, an AGU, and several memory units are used. ROM main intent is to store the twiddle factors. There are mainly two single ports of SRAM in NTT block. Here firstly two inputs are computed at same time by using the two NTT data there are NTT1 and NTT2. For the purpose of multiplication the NTT is used as inverse NTT and because of R input data is processed.

Addition and subtraction operations are performed in the Mul Mod unit. The result of this unit is processed to the buffer unit. Now the values are saved in ROM. Here point wise multiplication process is

performed in the NTT block and bits are computed depends on the current status of operation.

Fig. 1: Existed system

To relocate the data radix r is used and this will saves the memory temporarily. Basically there are four pipelined stages in the MulMod unit. To get conflict free address in the system buffer is used. But this system does not give effective results in terms of delay and time. Hence to overcome this, a new system is introduced which is discussed in below section.

### III. PROPOSED SYSTEM

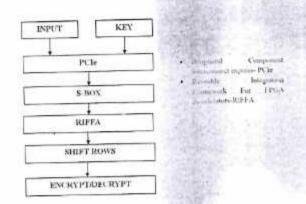

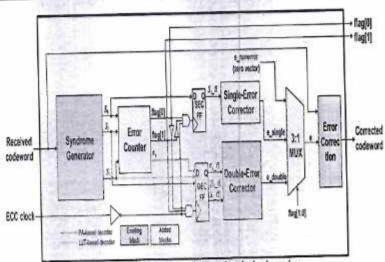

The below figure (2) shows the proposed system. This system will provide better security and resource efficiency compared to existing standards. RIFFA based Fully homomorphic encryption technique guarantee both privacy and integrity. The main intent is to increase the speed of operation. Initially, input bits and key is expanded serial by using PCIe. Next, bits are substituted using S-Box. After substitution by bytes, the bits will be reusable using INTERA. After reusable procedure shifting obligation is performed. Now these bits are included. Similarly, decryption process is to this operation. The description of block is given in detail manner.

Volume XIII, Issue II, February/2021

VIKAS GRAND OF INSTITUTIONS

NUMBER - 521 212

Vijayawada Rural, NTR Dist., A.P.

Fig. 2: PROPOSED SYSTEM

## A. SUBSTITUTE BYTES TRANSFORMATION (S-BOX)

The modified structure starts with changes in the Sub bytes step. The function of this step is to substitute data present in the S-box memory unit within the state by diverse data present in other memory unit. The dispersion of data in memory units creates the confusion. The main purpose of this Shannon's contents for scientific restraint arrangement is to stimulate security. The basic purpose of substitution of bytes is to secure information.

### B. ENCRYPTION

Encryption algorithm is a combination of complex mathematical functions which are used to encrypt the confidential information. Encryption key is a secret values that the sender utilizes as one of the inputs to the encryption algorithm in conjunction with plain text to generate a cipher text.

### C. REUSABLE INTEGRATION FRAMEWORK FOR FPGA ACCELERATORS (RIFFA)

Our goal is to expand the use of FPGAs as an acceleration platform by releasing, as open source, a no cost framework that easily integrates software on traditional CPUs with FPGA based IP cores, over PCle, with minimal custom configuration. RIFFA requires no specialized hardware or fee licensed IP cores.

# D. PERIPHERAL COMPONENT INTERCONNECT express (PCIe)

Peripheral Component Interconnect Express (PCIe or PCI-E) is a serial expansion bus standard for connecting a computer to one or more peripheral devices. PCIe provides lower latency and higher data transfer rates than parallel busses such as PCI and PCI-X.

### E. DECRYPTION

Decryption is taking encoded or encrypted text or other data and converting it back into text you or the computer can read and understand. This term could be used to describe a method of unencrypting the data manually or unencrypting the data using the proper codes or keys

### IV. RESULTS

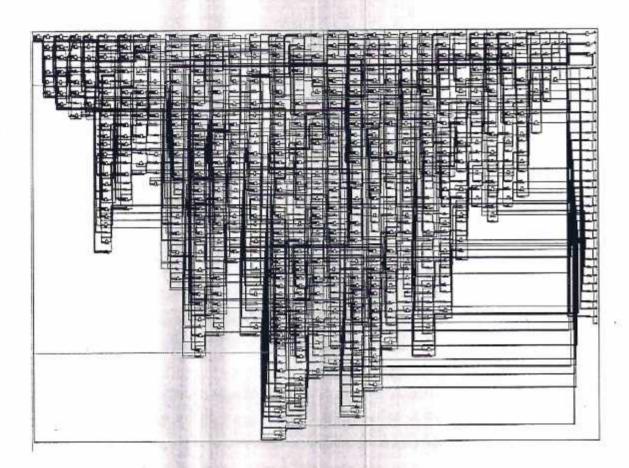

The below figure (3) & (4) shows the RTL schematic and technology schematic of RIFFA based homomorphic encryption and decryption system.

Fig. 3: RTL SCHEMATIC OF PROPOSED SYSTEM

phsilar

VIKAS GRUDOUT INSTITUTIONS NUMBERA - 521 212 Vijayawada Rural, NTR Dist., A.P.

Volume XIII, Issue II, February/2021

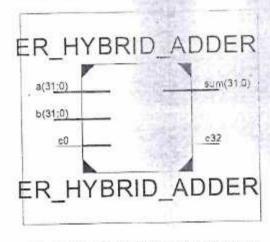

## DESIGN A HIGH SPEED EFFICIENT VLSI ARCHITECTURE OF E.R HYBRID ADDER

VALLURU PRAGATHE 'G SEKHAR REDDY

<sup>1</sup>M.Tech Scholar, Dept of ECE, Vikas Group of Institutions, Vijayawada, A.P, India

<sup>2</sup>Assistant Professor, Dept of ECE, Vikas Group of Institutions, Vijayawada, A.P, India

ABSTRACT: In this paper the Design a high speed efficient VLSI architecture of E.R Hybrid adder is implemented. Basically, adders are most commonly used in the applications of digital signal processing's, Microprocessors etc. Hybrid adder performed in three stages, they are propagator and generator stage, Internal carry generation stage and final sum stage. In this propagator and generator signals are generated by using propagation stage. Internal Carry generation stage will generate the carry. If any errors are occurred then error detection stage will detect the errors and error recovery stage will recover those output values. Final sum stage will take the output of hybrid adder and performs the operation and gives sum as output, At last from results it can observe that the propose system gives effective results.

KEY WORDS: Hybrid Adder, Internal Carry generation Stage, Final Sum Stage, propagator, Generator, VLSI.

### I. INTRODUCTION

Fastest technologies are developed in present days. In present days, reduction of device size, fast operation and low power consumption are required. The designing of low power VLSI system has more demand in mobile communication. Due to the device designed by designer with high speed, low power consumption and small silicon area, the device is available with low power.

ALU (Arithmetic logic unit) and FU (Floating point unit) are the main parts in computations [1]. Logical computations are addition, subtraction, multiplication, division and logical operations are AND, OR, INV and comparison which are processed by Arithmetic logic unit (ALU). Data path has an important role in digital signal processors and microprocessors because of some characteristics such as power consumption, speed of operation and die-area.

Data path contains complex operations are addition, division subtraction, multiplication [2]. The main important factor is data path performance which is affected by efficient hardware units of complex computations. In the data path addition is the important executed operation, addition operation contains binary adder to add given numbers. In complex computations such as decimal operations, multiplication and division, adders has important task [3]. To get data path efficiently, the implementation of binary adder should be efficient.

In central processing unit (CPU) crucial element is ALU (Arithmetic logic unit). An adder has important function in ALU and an adder performs not only addition but also performs multiplication, subtraction and decrement/increment. In ALU and general processors to get better performance, efficient adder is needed. From 1950s, for hardware implementation of VLSI arithmetic circuits, research started on efficient adder implementation. In control systems and digital signal processing main operation is the addition.

The properties of system or processor like accuracy and speed depends upon the performance of adder. To execute the addition of numbers, adder is used which is a digital circuit. Different processors and computers contains ALU in which adder is used. To reduce different parameters, different designs have been implemented based on parallel and serial structures. Four elementary operations are performed in binary addition.

The adders can be represented in many forms like BCD (binary coded decimal)

Volume XIII, Issue II, February/2021

FRENCIPAL/DIRECTOR

VIKAS GROUP OF INSTITUTIONS

NUNNA - 521 212

Vijayawada Rural, NTR Dist., A.P.

and excess-3 code; binary numbers are used in adders to perform the operation. Negative numbers are represented by ones complement or two's complement, for this adder is modified as adder-subtractor. More logic is required to represent signed numbers including basic adder [4-5].

To execute the addition operation, computers contain Arithmetic Logic unit (ALU) in which adders are mostly used. Graphics processing unit (GPU) and central processing unit uses the adders to decrease for the redundancy applications. In the adders first type is half adder it include two inputs and it provides two outputs such as carry and sum. Next one is full adders which include two inputs with carry input and it provides two outputs such as carry and sum. For single bit, both half adder and full adder is utilized. The full adder is coupled in parallel form to perform the multi bit addition operation.

### II. RELATED WORK

Binary addition performs the addition process based on the logic gates. Here single or two bit binary numbers are used. In binary addition process sum and carry are the outputs. Bit serial adder is the name of serial adder. Binary addition operation is performed in serial adder. Carry out and sum is the two outputs which are also single bit. Addition is executed by adding each bit from least significant bit to most significant bit and each bit has one clock cycle.

Full adder and one flip-flop are used in serial binary adder. Carry out signal for every clock cycle is given into flip flop. Thus the flip-flop generates the output as carry-in signal for next clock cycle. After completion of all bits of input operand, all bits of sum come from sum output.

1. The serial adder contains two binary digits along with the bit from

- previous addition. Pulse on clock input triggers the every addition.

- By using carry reset pin R, carry bit from addition at previous clock pulse is set to zero.

- The output can be complement of sum in some serial adders, it is optional.

Serial adder is a digital circuit which is a sequential circuit which contains full adder and flip-flop. At every clock cycle, previous bit addition result is taken and flip-flop stores the carry from full adder. Sum result is calculated and carry is given to flip-flop for next calculation. In this way, input data is given to full adder in serially, reading of results in serially, this is synchronized by clock.

BCD (binary coded decimal) adder is a digital circuit in which two BCD numbers are added in parallel and carry out and sum bits are generated. The result of sum will not be in BCD form when addition of two BCD digits is done.

The BCD result is correct in first example and BCD result is not correct in second example. BCD digits are represented from 0 to 9, to represent BCD numbers, four bits are required. But by using four bits, 16 values are represented. In the BCD digits extra six values are ignored because BCD digits are represented from 0 to 9. After addition, the result will not in BCD form when the result is greater than 9. It contains corrections to be done to obtain correct BCD results.

Half adder is used in digital electronics for the purpose of addition of two binary numbers. Full adder is used for the addition of 3-bit input sequence. If input sequence contain more number of bits, half adder and full adder does not satisfy the matter operation. These drawbacks are a fremme by Ripple carry adder. For the abstract of N-bit numbers, this type of the satenit is used in digital operations.

Volume XIII, Issue II, February 2021

PRINCIPALIDIRECTOR

WIKAS CITO CY OF INSTITUTIONS

ISLAND - 521 212

Vijayawada Rural, NTR Dist., A.P.

By using multiple full adders, logical circuit can be created for the purpose of addition of N-bit numbers. In each full adder, one of the sources of info is Cin which is taken care of from Cout of past adder. This kind of adder is known as Ripple-Carry Adder. Since each convey bit waves to next full adder. May be half adder is put in the principal full adder since first full adder contains Cin=0.

The Ripple carry adder circuit chart is straight forward, it creates quick plan time. In any case, the activity of wave convey adder is moderate on the grounds that each full adder ought to be hanging tight for convey bit which is originated from past full adder. By utilizing full adder circuit, door postponement can be determined. Three degrees of rationale are required in full adder. N full adders are required in n-bit Ripple convey adder.

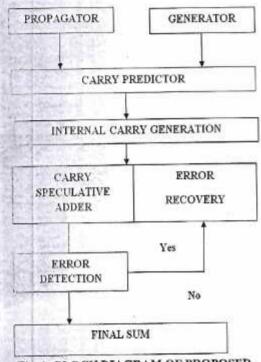

### III. PROPOSED SYSTEM

The below figure (1) shows the block diagram of proposed system. Hybrid adder performed in three stages, they are propagator and generator stage, carry generation stage and final propagation stage. In this propagator and generator signals are generated by using propagation stage. Internal Carry generation stage will generate the carry. Final sum stage will take the output of hybrid adder and performs the operation and gives sum as output.

Three stages are presented in the ER based Hybrid adder is explained in detail manner.

### 1. Propagator and Generator Stage:

In this stage, propagate signals and generate signals are manipulated to pair of each inputs A and B. Propagate signal and generate signal are represented as

Pi = Ai XOR Bi Gi = Ai AND Bi

### 2. Internal Carry Generation Stage:

In carry generation stage the calculation is performed based on the bits and carries obtained. The entire operation is performed in the form of parallel. Generate and propagate signals are obtained from the intermediate signals.

Fig. 1: BLOCK DIAGRAM OF PROPOSED SYSTEM

The below equations shows the propagate and generate signals:

Pi:j = Pi:k AND Pk-1:j

Gi;j = Gi:k OR (Pi:k AND Gk-1:j)

Black/gray cells implement the given two equations, which will be usually used in the following discussion on prefix trees.

### 3. Final Sum Stage:

In post processing stage the calculation is performed based on the input bits. From post processing stage sum and carry is generated. The below equations shows the sum and carry equations:

Ci = (Pi AND Cin) OR Gi

### Si = Pi XOR Ci-1

In applications of high speed circuits, very useful adder is PPA. PPA is designed based on the power and area.

Mon.

Page No:2042

Volume XIII, Issue II, February / 2021

PRINCIPAL/DIRECTOR

VIKAS GROUP OF INSTITUTIONS

EUINNA. - 521 212

Vilayawada Rural, NTR Dist., A.P.

Structure delay= log2 n

Number of computation nodes= [(n) (log<sub>2</sub> n)-n+1]

### IV. RESULTS

The below figure (2) shows the RTL schematic of proposed system, here a and b are the inputs and cout is the output.

Fig. 2: RTL SCHEMATIC OF PROPOSED SYSTEM

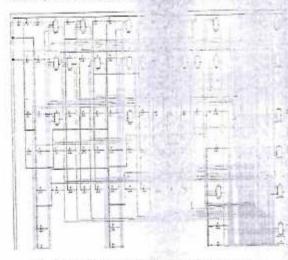

The below figure (3) Technology schematic of proposed system. RTL schematic is the combination of Look up tables, truth tables, K-MAP and equation.

Fig. 3: TECHNOLOGY SCHEMATIC OF PROPOSED SYSTEM

Fig. 4: OUTPUT WAVEFORM OF PROPOSED SYSTEM

Total S.199nz (D.745ns logic, T.45ins posts)

(3.18 logic, 90.56 routs)

Trues clock Domains Report:

Total MINAL tips to Xet completion: 12.00 secs

Total GW time to Ket completion: 11.63 secs

Total Security 1020 is 451552 bildwyses

times Adjective Of 0 fictored)

Total Security 1020 is 35 i 0 filtered;

to 15 termings: 35 i 0 filtered;

to 15 termings: 3 i 0 filtered)

Fig. 5: SYNTHESIS REPORT OF PROPOSED SYSTEM

### V. CONCLUSION

Hence in this paper Design a high speed efficient VLSI architecture of E.R Hybrid adder was implemented. The internal carry generation stage plays important role in entire operation. Generate and propagate signals are generated to increase the speed of operation. This design is simulated in Xilinx software. Hence from simulation results, it can observe that Hybrid adder gives effective result.

Volume XIII, Issue II, February/2021

PRINCIPALIDIRECTOR

VIKAS GROUP OF INSTITUTIONS

EUNNA. - 521 212

Vijayawada Rural, NTR Dist., A.P.

### VI. REFERENCES

[1] Vishwa Shah, Urvisha Fata, Jagruti Makwana, "Design and Performance Analysis of 32 Bit VLSI Hybrid adder", Proceedings of the Third International Conference on Trends in Electronics and Informatics (ICOEI 2019) IEEE Xplore Part Number: CFP19J32-ART; ISBN: 978-1-5386-9439-8.

[2] R. Zimmermann, "Binary adder architectures for cell-based VLSI and their synthesis," Ph.D. thesis, Swiss Federal Institute of Technology, (ETH) Zurich, Zurich, Switzerland, 2017, Hartung-Gorre Verlag.

[3] R. P. Brent and H. T. Kung, "A regular layout for parallel adders," *IEEE Trans. Comput.*, vol. C-31, no. 3, pp. 260–264, Mar. 2014.

[4] P. M. Kogge and H. S. Stone, "A parallel algorithm for the efficient solution of a general class of recurrence equations," *IEEE Trans. Comput.*, vol. C-22, no. 8, pp. 786-793, Aug. 2007.

[5] J. Sklansky, "Conditional-sum addition logic," *IRE Trans. Electron. Comput.*, vol. EC-9, pp. 226–231, Jun. 2006.

[6] T. Han and D. A. Carlson, "Fast area-efficient VLSI adders," in Proc. IEEE 8th Symp. Comput. Arith. (ARITH), May 18-21, 2004, pp. 49-56.

[7] R. E. Ladner and M. J. Fischer, "Parallel prefix computation," J. ACM, vol. 27, no. 4, pp. 831–838, Oct. 2003

[8] Bernd Becker, "Efficient testing of optimal time adders," Proc. IEEE, Vol. 37, pp. 1113-1120, Sept. 2002.

[9] I. Flores, "The Logic of Computer Arithmetic," Chaps. 4, 5 and 7, Englewood Cliffs, N.J. Prentice Hall, 2002.

[10] O.L. Macsorley, "High-Speed Arithmetic in Binary Computers," Proc. IRE, Vol. 49, pp. 67-91, Jan. 2001.

[11] J. Slansky, "Conditional-Sum Additional Logic," Proc. IRE Trans. Electronic Computers, Vol. 9, pp. 226-231, June 2000.

[12] J.B. Gosling, "Conditional-Sum Early Completion Logic," IRE Trans. Electronic Computers, Vol. 59, 2000, pp. 226-231.

[13] N.M. Martin and S.P. Hunagel, "Conditional-Sum Early Completion Adder Logic," IEEE Trans. Vol. c-29, pp. 753-756, Aug. 2000.

[14] Z. Navabi and F.H. Hill, "User manual for AHPL Simulator," Tucson, Arizona, University of Arizona.

[15] F.J. Hill, and G.R. Peterson, "Digital Systems," Chap. 14, N.Y, John Wiley & Sons, Inc, 2000.

VALLURU PRAGATHI Completed B.Tech from Vikas college of , engineering and technology, Vijayawada, Andhra Pradesh, India and pursuing M.Tech from Vikas group of institutions, Andhra Pradesh, India. Her M.tech specialization is VLSI Design.

<sup>2</sup>G SEKHAR REDDY completed B.Tech at Sana Engineering College-JNTUH, Andhra Pradesh, India. M.tech from Gitam University, Andhra Pradesh, India. Pursuing Ph.D Kalinga University Raipur, India, He has 10 years of teaching experience and working as Assistant professor at Vikas group of institutions, Vijayawada, A.P. India. His area of interest is Low Power VLSI.

Merlet

Volume XIII, Issue II, February/2021

PRINCIPALIDIRECTOR

VIKAS GROUP OF INSTITUTIONS

INUNNA - 521 212

Vijayawada Rurai, NTR Dist., A.P.

## Implementation of 32\*32 Dadda Multiplier

<sup>1</sup>Rajani Manukonda, PG Scholar, Department of ECE, Vikas Group of Institutions, JNTUK, Andhra Pradesh, Email id: manukondarajani630@gmail.com

<sup>2</sup>G Sekhar Reddy, Assistant Prof, Department of ECE, Vikas Group of Institutions, JNTUK, Andhra Pradesh, Email id: gaddamsekharreddy@gmail.com

ABSTRACT: In this research paper, the technique for the design of a fast multiplier is proposed by using two different techniques. A 4:2 compressor is used for power-efficient row compression in the proposed model, whereas for faster final summation, a carry-select adder has been used. Based on the above technique, a 16-bit Dadda-multiplier is proposed and its performance is analysed by comparing it with the standard 16- bit Dadda-multiplier which normally uses carry-look ahead adder. The time delay of carry-select adder is improved when compared to carry propagate adder. The result depicts that the proposed 16-bit Dadda-multiplier is 4.85% power efficient and 63.4%-time delay is improved. The simulation of the proposed multiplier is carried out using Verilog HDL in Xilinx ISE Design Suite 14.7.

Keywords— ALU, Dadda-multiplier, 4:2 compressor, carry select adder, carry propagate adder, Wallace-multipliers, half adder, full adders

### I. INTRODUCTION

Multiplier is one of the most important circuits for designing computers and computing devices. The Dadda technique for partial product reduction is based on the idea of 'avoid use of full adder.' But the use of full adder is more regular in other Wallace tree multipliers. This paper presents a modified Dadda technique based on the idea of 'prefer the use of full adder over the use of half adder.' Only the last stage that is 'three to two reductions' is the exception. This idea used in the modified technique makes it more regular and simple. Hence, based on the idea, it is named as 'Full-Dadda.' The fact behind saying this technique an alternative approach is that this technique results in same number of full adders, half adders, same size of final carry propagation adder and same number of compressors (adders) at each stage as required in the Dadda technique. Therefore the proposed multiplier can be used in place of Dadda multiplier in all its applications. This paper presents a comparative performance analysis of the proposed multiplier with the Dadda multiplier. For this comparison each multiplier with different operand sizes is taken. The main disadvantages of the Dadda multiplier are: (i) it is less regular, (ii) more complex and (iii) it reduces less number of bits at early stages of reductions. The proposed 'Full-Dadda' multiplier is more regular, simple and reduces more number of bits at early stages of summand reduction. In section 2, there is brief overview of literature and in section 3; there are general rules and equations for reduction scheme and number of hardware components respectively. The comparison between multipliers is arranged in five sub-sections under section.

Page | 273

PRINCIPALIDIRECTOR

VIKAS GROUP OF INSTITUTIONS

HUNNA - 521 212

Vijayawada Rural, NTR Diet., A.P.

Copyright @ 2021 Authors

### II. Literature Survey

A. Some Important points

The parallel multipliers are faster and more fancied [1]. There are many ways and schemes available for multiplication [1], such as Array multiplication scheme, Booth multiplication and Vedic multiplication etc. Among these schemes, the tree multiplication scheme is one of the most popular schemes. [1,2,3,4,5,6]. The most popular multiplier among tree multipliers is the Dadda multiplier [2]. A Reduced Area multiplier is also the best optimized multiplier in terms of Area if interconnects are properly managed [3]. The basic steps involved in a tree multiplication scheme, first used by Wallace [6] in 1963 are:

- 1) Generation of the partial products [3] (or summands [5, 6] or matrix of partial products [1]).

- 2) Partial products reduction: reduction in column height by using pseudo adders (there are many parallel addition schemes [8] and partial product reduction schemes [9] implemented by using pseudo additions such as conditional sum addition [7] etc.).

- 3) Use of final CPA (carry propagation adder): After the last stage of column-height reduction (remaining bits in a column are only two), there is a need of final addition of two rows to obtain final product of multiplied operands. The size and type of final CPA used plays an important role in determining overall performance such as delay, area and power consumption [2, 3, 5].

B. Dadda Multipliers

Dadda method for partial product reduction uses only necessary reduction determined by the Wallace table shown in table 1 [2, 3, 4]. It uses an approach to increase the number of half adders and to decrease the number of full adders required for overall reduction of partial products. The detail of Dadda technique is given in the references [2, 3, 4, 5, 9]. The Dadda method keeps as these are all right columns having height less than or equal to the necessary bits required at a stage after reduction. This is repeated at every stage.

Table1: Number of reduction stages for Dadda multiplier

| Number of Stages |

|------------------|

| Remarks III      |

| 2                |

| 3                |

| 4                |

| 5                |

| 6                |

| 3011207          |

| 8                |

| 9                |

| 10               |

|                  |

Page | 274

Copyright @ 2021 Authors

VIKAS GRULP OF LATATIONS RUNNA - 521 212 Vijayawada Rurai, NTR Dist., A.P.

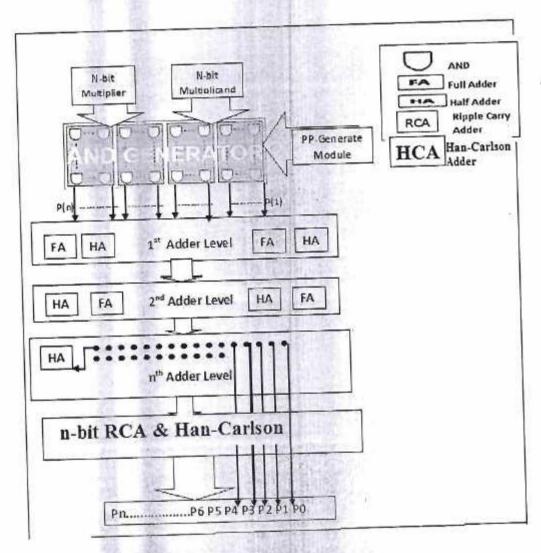

## III. PROPOSED METHOD

Two of the most well-known column compression multipliers have been presented by Wallace [5] and Dadda [6]. Both architectures are similar with the difference occurring in the procedure of reduction of the partial products and the size of the final adder. In Wallace's scheme, the partial products are reduced as soon as possible. On the other hand, Dadda's method does minimum reduction necessary at each level and requires the same number of levels as Wallace multiplier. As a result, final adder in Wallace multiplier is slightly smaller in size as compared to the final adder in Dadda multiplier. The Block diagram of proposed energy efficient column compression multipliers (Wallace/Dadda) is shown in Fig.

Fig. 1. Block diagram of proposed energy efficient n-bit column compression multiplier

Page | 275

Copyright @ 2021 Authors

PIKAS GROUP DE LA STATUTIONS NUMBAR - 521 212 Mjayawada Rural, NTR Dist., A.P. Dogo Rangsang Research Journal

ISSN: 2347-7180

UGC Care Group I Journal Vol-08 Issue-14 No. 03: 2021

A Wallace/Dadda multiplier is usually composed of threeparts (or modules)

Partial product generate module

A Half Adder (HA) and Full Adder (FA) tree toreduce the partial products matrix to anaddition of only two Operands.

Han-Carlson and Ripple Carry Adder (RCA) for thefinal computation of the binary result.

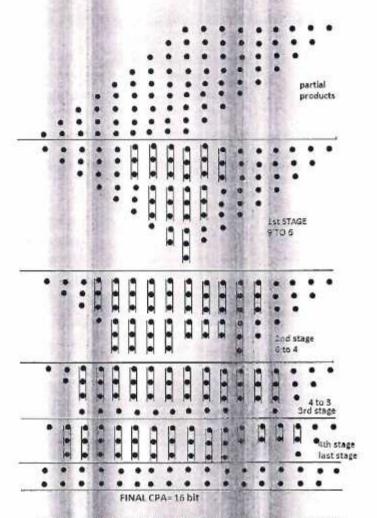

In the proposed energy efficient multipliers, the reduction partuses half-adders, full-adders and ripple carry adders; each partial product bit is represented by a dot as shown in Fig 3.1.Reduction is performed depending on the number of elements in that particular column of the group. Three dot products issued to represent a FA, whereas only two dot products is used To represent a HA. If a column has only one element then that is passed on to the next stage without any reduction. If the last group of a stage contains less than three rows then no reduction is performed on that group. The last part performs the function to add the remaining two rows using an exact RCA & exact Han-Carlson adder to compute the final binary result in sub threshold regime. All the standard cells are same in both 8x8column compression Wallace & Dadda multipliers, Static CMOS logic family is used for AND gate, HA, FA and partial product generation module in sub-threshold regime.

## ASIC IMPLEMENTATION

The complete ASIC implementation of the proposed design isalso done which follows the cadence design flow. The proposed design has been developed using Verilog-HDL and synthesized in Encounter RTL compiler using typical libraries of 45 nm technology. The test bench is created for simulation and logic verification by Model-Sim simulator. The CadenceSoC Encounter is used for Placement & Routing (P&R). Parasitic extraction is performed using Encounter Native RC extraction tool. The extracted parasitic RC (SPEF format) is back annotated to Common Timing Engine in Encounter Platform for static timing analysis. Results obtained from both tools are analyzed and compared for semi-custom design verification shown.

Page | 276

Copyright @ 2021 Authors

VIKAS GROUP OF INSTITUTIONAS

Fig 2 RTL Schematic 32\*32 Dadda Multiplier

Page | 277

Copyright @ 2021 Authors

VICTOR POLICIPECTOR

VILLA GRUCE OF INSTITUTIONS

NUMBA - 521 212

Vijayawada Rural, NTR Dist., A.P.

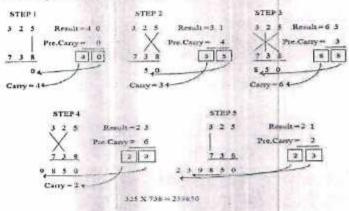

Fig 3: Proposed Multiplier Reduction Scheme

The ASIC Implementation is to be done to differentiate the performance evaluation of the Wallace and Dadda multipliers in sub-threshold and super-threshold regime. The stimulation results were carried out of two 8x8Wallace & Dadda multiplier designs using RCA and two 8x8Wallace & Dadda multiplier design using HCA in sub-threshold regime. The designed energy efficient multiplies operates at 0.4V. In fact, in addition to normal transistors, circuits are tested in corner cases with fast and slow transistors and their combinations too. In each stage one of the components FF, SS, FS, and SF is replaced instead of normal transistors in circuit and is purposed in each circuit function. Since the delay of multiplier circuit is proportional to the logarithm of the number of bits in the multiplier and also delay of used standard cells. To measure the critical path delay and to verify the functionality of proposed Wallace/Dadda multipliers, n-no. Of test patterns have an applied to the multiplier. The worst delay has been observed for the inputs from 1111111111000011

Copyright @ 2021 Authors

Page | 278

VIKAS GRUEP OF ANSTITUTIONS NUNNA - 521 212 Vijayawada Rural, NTR Diat., A.P.

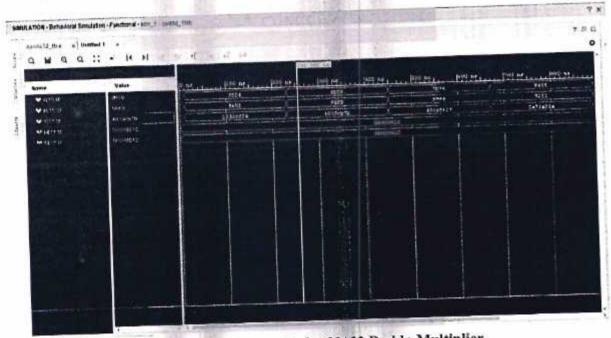

#### SIMULATION RESULTS IV.

The proposed design has been developed using Verilog-HDL and synthesized in Xilinx 14.5 tool and the same tool was used for Placement & Routing (P&R). Results obtained from the tool are analyzed and the schematic is shown in the below figure.

Fig 4 simulation results for 32\*32 Dadda Multiplier

### V CONCLUSION

In this paper, the 16x16 Dadda multipliers have been implemented at 0.4 volt power supply. The main focus of this paper was to optimize overall power delay product. We have also optimized the no. of transistor in the design. The simulated result shows that the proposed Dadda have improved results as compared to existing published results. Thus the design of Dadda multiplier has improved power, performance.

## VI. FURTHERSCOPE

As can be seen from the results obtained by Dadda multiplication scheme, this approach is further extended to perform the multiplication of higher bits (i.e., 32 bit × 32 bit, 64 bit × 64 bit and so on). The power consumption and area estimate are further reduced by implementing the final adder with look ahead carry generation logic (look ahead carry adder).

### VII. REFERENCE

[1]. High-Speed Parallel Multiplication Scheme," IEEE TRANSACTIONS ON COMPUTERS,

[2] R. S. Waters and E. E. Swartzlander, "A reduced complexity wallace multiplier reduction," IEEE Transactions VOL. C-26, NO. 10, OCTOBER 1977 on Computers, vol. 59, no. 8, pp. 1134-1137,

Page | 279

Copyright @ 2021 Authors

VIKAS GROUP OF ....NUNNA

Vijayawada Rural, NTR Dist., A.P.

## UGC Care Group I Journal Vol-08 Issue-14 No. 03: 2021

## Dogo Rangsang Research Journal ISSN: 2347-7180

[3] K. C. Bickerstaff, M. J. Schulte, and E. E. Swartzlander, Jr., "Reduced Area Multipliers," in Proceedings of the 1993 International Conference on Application Specific Amy Processors, pp. 478-489, IEEE, 1993. The Proposed Full-Dadda Multipliers (IJIRST/ Volume 4 / Issue 11 / 017)

[4] K'Andrea C. Bickerstaff, Earl E. Swartzlander, Michael J. Schulte, "Analysis of Column Compression

Multipliers",15th IEEE Symposium on Computer Arithmetic Proceedings, pp 33-39, 2001.

[5] A. Habibhi and P.A. Wintz "Fast Multipliers," IEEE Transactions on Computers, Vol. C-19, pp. 153-157,

[6] C. S. Wallace, "A suggestion for a fast multiplier," IEEE Transactions on Electronic Computers, vol. EC-13,

[7] J. Sklansky, "Conditional-sum addition logic," IRE Transactions on Electronic Computers, vol. EC-9, pp.

[8] R. P. Brent and H. T. Kung, "A regular layout for parallel adders," IEEE Transactions on Computers, vol. C-

[9] Wesley Chu, Ali I. Unwala, Pohan Wu, and Earl E. Swartzlander, Jr., "Implementation of a High Speed Multiplier Using Carry Lookahead Adders," 978-1- 4799-2390-8/13, 2013, IEEE. K'Andrea C. Bickerstaff, Earl E. Swartzlander, Michael J. Schulte, "Analysis of Column Compression Multipliers",15th IEEE Symposium on Computer Arithmetic Proceedings, pp 33-39, 2001.

[10] A. Habibhi and P.A. Wintz "Fast Multipliers," IEEE Transactions on Computers, Vol. C-19, pp. 153-157,

[11] C. S. Wallace, "A suggestion for a fast multiplier," IEEE Transactions on Electronic Computers, vol. EC-13,

[12] J. Sklansky, "Conditional-sum addition logic," IRE Transactions on Electronic Computers, vol. EC-9, pp.

[13] R. P. Brent and H. T. Kung, "A regular layout for parallel adders," IEEE Transactions on Computers, vol. C-

[14] Wesley Chu, Ali I. Unwala, Pohan Wu, and Earl E. Swartzlander, Jr., "Implementation of a High Speed Multiplier Using Carry Lookahead Adders," 978-1-4799-2390-8/13, 2013, IEEE.

Rajani Manukonda, Pg scholar, Vikas Group of Institutions, JNTUK, Andhra Pradesh, Specialization in VLSI Design

G SEKHAR REDDY, M.TECH IN GITAM UNIVERSITY, ASSISTANT PROF, AREA OF INTEREST :LOW POWER VLSI, Vikas Group of Institutions, JNTUK, Andhra Pradesh

Page | 280

Copyright @ 2021 Authors

PRINCIPALIDIRECTOR VIKAS GROUP OF INSTITUTIONS NUNNA - 521 212 Vijayawada Rural, NTR Dist., A.P.

MAS lots

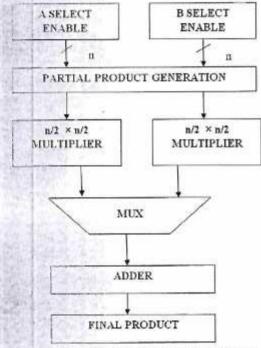

# DESIGN AND IMPLEMENTATION OF HIGH EFFICIENT DELAY UTILIZATION OF (n/2) PARALLEL MULTIPLIER

SUNKARA SRIDEVL GALKHAR REDDY

<sup>1</sup>M.Tech Scholar, Dept of ECE, Vikas Group of Institutions, Vijayawada, A.P. India <sup>2</sup>Assistant Professor, Dept of ECE, Vikas Group of Institutions, Vijayawada, A.P. India

ABSTRACT: In this paper, design and implementation of high efficient delay utilization of (n/2) parallel multiplier is done. Basically, multipliers are key arithmetic circuits in many of these applications including digital signal processing (DSP). This n/2 parallel multiplier uses adder that limits its carry propagation. First the alignment of partial products generator will be done. After that partial products takes this registers and generates the propagate and generate signals. After this  $n/2 \times n/2$  multiplication operation is performed. Now this bits perform the addition operation and gives the final product. Hence this paper reduces the delay in effective way.

Key Words: VLSI, Digital signal processing (DSP), Partial products, Multiplexer and Adder.

### I. INTRODUCTION

Basically, in communication systems like error correction codes and cryptography, finite field is most widely used. Arithmetic operations are performed using the field elements. Two basis are normally used to implement a system that is normal basis and polynomial basis. Normal basis is used to implement the hardware and perform the low cost squaring operations. In the same way, polynomial basis is used to implement the software and in the same way this also performs the low cost squaring operations [1]. Accuracy could be compromised to a defined extent in most of the present-day applications like image recognition and processing. Multiplier is the basic building block of such applications which involve a lot of mathematical processing. This leads to a win-win balancing between the energy consumed by the circuit and the required accuracy.

The energy consumed by any system is directly proportional to the multiplication accuracy of those systems. If a system requires high accuracy then it consumes more energy and vice versa. Also, there could be section or module of that systems which needs lesser accuracy than other parts of the system. If the accuracy is kept constant across all such modules it greatly increases the amount of energy consumed by the overall system. However, if the accuracy of the multiplier is characterized to change as per the need of that particular module or section of the entire system, this would have a great impact in reducing the amount of energy consumed by the system [2].

This method of configuring and adjusting the accuracy of a multiplier based on the requirement of the system or application is achieved using different adder sub module of the multiplier module to characterize the accuracy based on the approximation technique. There should be reconfigurable multipliers in various program stages or applications [3]. So, in this paper we designed a multiplier which has an accuracy decided on the go based on the requirement of the application.

Montgomery's multiplier is classified into three types, they are bit-serial, bit-parallel, and digit serial architectures. Bit-parallel shape is rapid; however it's far steeply-priced in phrases of vicinity. Bit-serial structure is region efficient, but it's far too sluggish for plenty packages. The digit-serial structure is flexible which may change the space and velocity, consequently, it

Volume XIII, Issue II, February/2021

F NCIPALIDIRECTOR

VIKAS GROUP OF INSTITUTIONS

NUNNA - 521 212

Vijayawada Rural, NTR Dist. A.P.

achieves a moderate pace, reasonable price of implementation and hence it is most appropriate for practical use. Montgomery presented a technique for figuring modular multiplication productively. He introduced to move the portrayal of numbers from the Zn to an alternate area, called Montgomery Residual portrayal or Montgomery Domain [6-7].

Here for the purpose of security, the computers and communication system brought with a demand from private sector [4]. The Montgomery multiplication is the calculation that permits effectively for registering. The expense of the particular duplication is equivalent to three whole numbers which increases in addition to the expense of the change in the Montgomery area. Yet, in the event that the large scale task is an exponentiation, at point the change cost is insignificant contrasted with the quantity of augmentations executed in the Montgomery area. In the process of Montgomery multiplication, pre-processing unit and post-processing units are used [5]. The pre-processing unit produces N-Residue operands and in the same way post processing unit will eliminate the constant factor 2n. Hence to form N-Residue modular system, the operands exponentiation is used.

Here for the purpose of supplanting division activities, shifting tasks are used. After the shifting process the least critical bits will remain zero. Now to eliminate these bits in the modular multiplication, add products are used. After the process of eliminating the bits, the remaining bits are augmented in the Hence from this it can multiplicand. observe that the process of multiplicand is completed. Now the output is obtained after the subtraction of bits. Here if the bits are increased then Montgomery bits also increases. At last the multiplicand bits are controlled without the use of subtraction calculation.

## II. LUT BASED MULTIPLIER

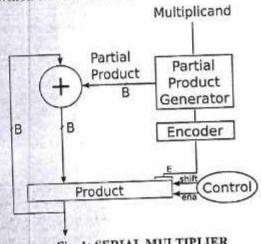

The below figure (1) shows the block diagram of serial Multiplier. The entire flow chart performs its operation in four stages which are discussed below:

Fig. 1: SERIAL MULTIPLIER

This calculation begins by putting away item esteem in memory where multiplier is 2 and multiplicand is 0, 1, 2, 3, 4, 5, 6, and 7. The Address is the estimation of Multiplicand.

Stage 1: If the Multiplier is 2 and multiplicand is any an incentive from the range 0-7, at that point the item esteem put away at that specific memory area (characterized by multiplicand) is net yield. In any case, if the Multiplier is other than 2 and multiplicand is from 0-7 then re-look in memory to discover if the necessary yield is as of now determined. In the event that indeed, take the yield from that specific location.

Model: how about we guess the multiplier be 2 and multiplicand be 5, at that point 2x5=10 and 10 (10101)2 is as of now put away at memory area 5. In any case, if the multiplier isn't 2 and item esteem is as yet accessible in memory (like 3x4=12 (1100)2

Volume XIII, Issue II, February/2021

LIDIRECTOR VIKAS GROUP OF INSTITUTIONS NUNNA - 521 212 Vijayawada Rural, NTR Dist., A.P.

previously put away at area 6), at that point essentially get the item esteem at yield put away at that specific area.

Stage 2: If the Multiplier is other than 2 and the worth isn't accessible in memory; search for close by esteem (one less or one more prominent of anticipated item) and flip the last piece. Model: 3x5=15 and this worth isn't accessible in memory, so take the close by esteem 14 (1110)2 and flip the last piece to make 14(1110)2 to 15(1111)2.

Stage 3: If the close by esteem is absent, search for any least factor of the item esteem and annex the bit(s) in the last. For example,4x5=20. Here 10 (1010)2 is minimal factor of 20 (10100)2. So take the yield 10 accessible at memory area 5 and annex zero in the last to get the twofold of 10 that is 20. So also, assume multiplier is 3 and multiplicand is 7. Here the item would be 21(10101)2. Be that as it may, 21 are not accessible in memory. Along these lines, this can be accomplished by taking 10 (1010)2 at the yield and afterward annexing 1 in the last. This will change the 10 (1010)2 in to 21(10101)2.

Stage 4: If above advances doesn't give the necessary yield, attach two bits in the last to get the necessary information. For instance, if there should be an occurrence of 7x5 coming about item esteem is 35 (100011)2 and when we annex (11)2in the last to 8 (1000)2, we can without much of a stretch get the yield 35(100011).

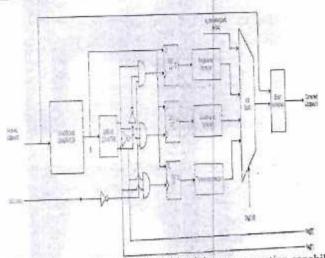

### III. PROPOSED SYSTEM

The below figure (2) shows the block diagram of serial multiplier. The entire system is divided into following modules. The following modules are inputs A and B, partial products, n/2 multiplier, multiplexer. adder and final product. This operation is mainly used in the coprocessor in parallel format. This system provides the

functionality for coprocessor. First the alignment of partial products generator will be done. After that partial products takes this registers and generates the propagate and generate signals. After this n/2 × n/2 multiplication operation is performed. Now this bits perform the addition operation and gives the final product.

Fig. 2: BLOCK DIAGRAM OF SERIAL MULTIPLIER

Here firstly, the operands are loaded in the multiplier. The arithmetic operations like addition and multiplication operations are performed. The obtained result of this will be saved in the barrel shifter. Here irreducible polynomial function is not used in the system. The main intent of register multiplier is to store the bit representation and give polynomial output a(t). Here parallel load operation is performed in the most significant bit position. In the same way left shift operations are performed in MSB bit.

The B select enable is used b(t) value to store the value in register. The parallel load operation is also applied in the multiplicand.

Mislar

Page No: 2947

Volume XIII, Issue II, February/2021

VIKAS GROUP OF INSTITUTIONS NUNNA - 521 212 Vijayawada Rural, NTR Dist., A.P. The obtained value is stored in the register. The right shift operation is performed in the multiplicand register block, crypto core processor is used to transfer the data in multiplicand register.

The result A select enable and B select enable is processed to the partial product generator block. The both A select enable and B select enable values are assigned in the barrel shifter blocks. The obtained values in the propagator and generator block will generate the signals. This block will perform the addition operation.

An adder is a digital circuit that performs addition of numbers. A multiplexer or mux is a combinational circuits that selects several analog or digital input signals and forwards the selected input into a single output line.

Final product is the combination of output. Where all bits gets mixed to get the final output. Hence from results it can observe that the proposed system, will reduce the delay and memory usage in very effective way.

### IV. RESULTS

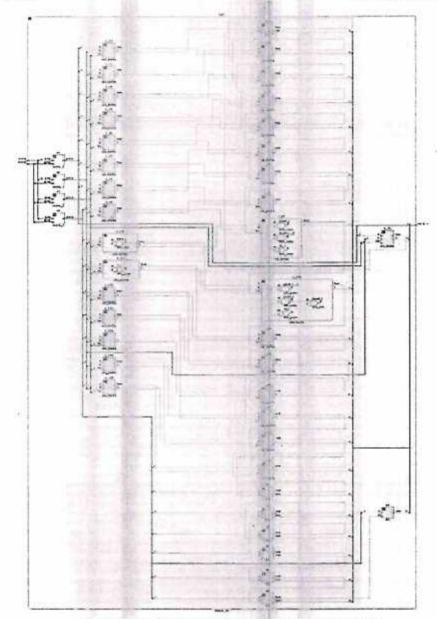

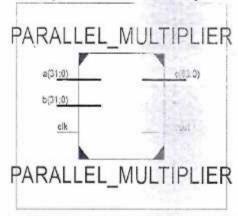

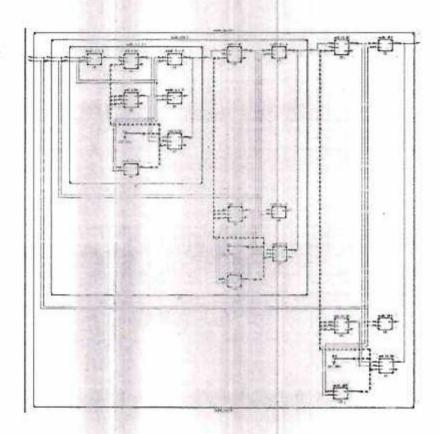

The below figure (3) shows the RTL schematic of proposed system, here a and b are the inputs and cout is the output.

Fig. 3: RTL SCHEMATIC OF PROPOSED SYSTEM

The below figure (4) Technology schematic

Volume XIII, Issue II, February/2021

of proposed system. RTL schematic is the combination of Look up tables, truth tables, K-MAP and equation.

Fig. 4: TECHNOLOGY SCHEMATIC OF PROPOSED SYSTEM

| 77     | VAss                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 外形容 (現形容 [現現名 [現現名 [現現名 [現現名                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 42     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | THE REAL PROPERTY AND ADDRESS OF THE PARTY AND |

| 推相性    | Stamped                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Shipping a Community                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 福州     | SECRETOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | WITH THE ROOM AND THE ROOM THE |

| 著書詞    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | processors and the filtrens of a gills                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

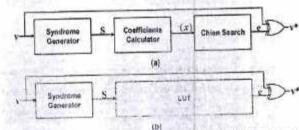

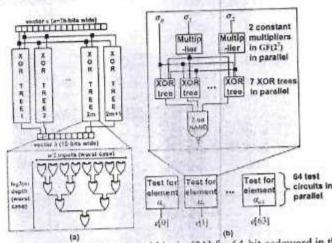

| ig sof | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |